Мой глитч.

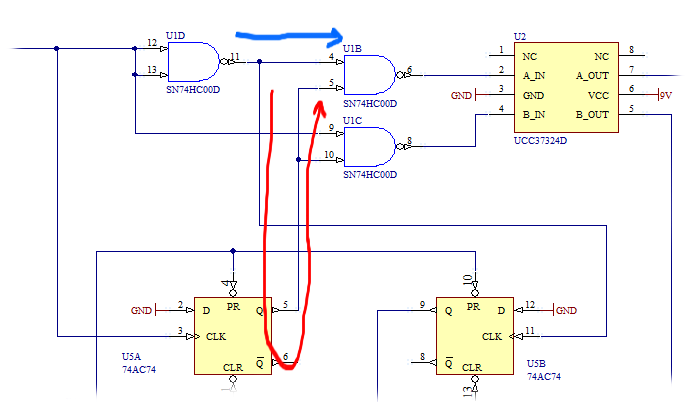

Посмотрите на схему:

Естественно, сходу не понятно, что тут не так, но я помогу.

Сигнал, который проходит по красной стрелке прекращает подачу синего сигнала на вход U2. Но на красной ветке есть задержка, возникающая за счет того, что сигнал проходит через целых два триггера. Разница в задержках вышла порядка 10нс.

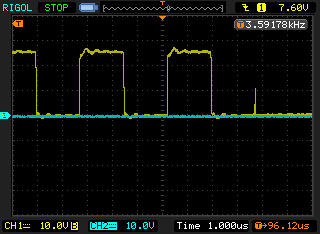

Вот, что получается на выходе схемы:

Не смотря, на то, что на выходе стоят неповоротливые силовые компоненты, разница в задержках таки проникает на выход. Вот та последняя иголка – и есть глитч.

Тут мне очень крупно повезло, ведь у последующего куска схемы нет “памяти” и эта палочка бесследно пропадет, слегка нагрев транзисторы. Если бы там стоял счетчик или еще что ни будь в таком духе, эту иголку наверняка бы посчитало.

Если бы процесс был непериодический, то найти такую иголку было бы совсем сложно.

Что делать, если проморгал такую ситуацию? Решение тут обычно нетривиальные: можно поставить RC (или просто С, речь ведь идет о наносекндах) цепочку.

У меня-же получилось обойтись малой кровью и заменить 74HC74 на 74AC74 – он намного быстрее и успевает сработать еще до того, как И-НЕ переключились.

Это – довольно простой случай. В более высокочастотной технике, глитчи появляются из-за задержки распространении сигнала по дорожкам платы. Именно для того, чтобы этого не произошло, делают “змейки“ на платах.

Было такое, когда паял первый Синклер. поставил то, что нашел.

Не знал я тогда что схема капризная и смешивание разных серий микросхем породит неслабые глюки. Запустил я его только через месяц после сборки.

У ус37324, согласно ДШ, задержка по фронту ==25 наносек, шпилька в 10 нан не должна пролазить на выход драйвера.

Это — задержка. То-есть, шиплька в 10 нс вылезет на выходе но с задержкой в 25нс 🙂

Кстати, я до сих пор так и не знаю вот такую штуку — как определить, на сигнал какой длительности компаратор сработает. У компараторов указывается propagation delay — но это ничего не говорит о скорости срабатывания, которая должна, по идее, значительно превышать задержку распространения.

>То-есть, шиплька в 10 нс вылезет на выходе но с задержкой в 25нс

Ага… Правильно. Там другой параметр учитывается: время фронта У вых, т.е. если входной сигнал короче фронта У вых, то на выходе импульса правильной амплитуды не получится…

У этого явления есть название — это гонка сигналов. Сильно досаждает разработчикам на элементах низкого уровня интеграции. Один из способов борьбы — тактируемые схемы, а применение RC цепочек — это не очень хорошо (они же нестабильные по температуре, задержка также зависит от от уровня срабатывания последующего элемента, который тоже может плавать, возможна даже возникновение генерации на ВЧ в последующем элементе, если фронт сигнала на его входе будет слишком плавный, а сам элемент достаточно быстродействующий…). Поэтому и стараются избегать применение RC цепочек по цепям распространения сигналов, повторяемость схемы из-за этого становится недостаточно высокой. Это я помню еще с курса лекций по цифровой схемотехнике 🙂 Всем удачи в разработках!

Во первых схема не дорисована! Не схема, а какой-то огрызок.

Во вторых совершенно не понятно (возможно из-за недоросованности), как на выход вообще пролезло столько импульсов, ведь первый же фронт должен записать в U5A нулевое значение, которое тут же запретит дальнейшее распространение входного согнала!

Вцелом же можно сделать вывод о том что схема спроектирована принципиально неверно из-за чего и получаются всякого рода глютчи.

>Во первых схема не дорисована!

Естественно, нарисовано толькото, что важно для понимания.

>первый же фронт должен записать в U5A нулевое значение

только если пин nPR не держится в нулевом состоянии, но это тут не важно.

>из-за чего и получаются всякого рода глютчи.

не неверно, а с ошибкой. Если бы ошибки не было, то я бы про это не писал.

Да но тут принципиально неверно указана ошибка — применение «медленной» логики, а решение — применение более скоростной. Наверняка можно было решить проблему в пределах «медленной» логики, с применением идеологически верной схемотехники.

Совершенно согласен с Magnum по поводу применения «медленной» и «быстрой» логики. Так не надо делать никогда! Нужно правильное схемотехническое решение, с учетом особенностей применяемых элементов. Например, можно применить парафазные сигналы (как например в 500 серии есть прямые и инверсные выходы у одного и того же элемента, или выходы Q и не Q D-триггеров 74 серии), вот здесь и нужен подобный вариант — «прямой» сигнал на входе U1C и его инверсия на входе U1B, но этот сигнал должен прийти либо с одного и того же элемента, либо с одинаковыми задержками по разным путям следования… В этом-то и заключается сложность создания надежных схем, надо уметь обходить такие неприятные моменты. Я бы применил либо тактируемые схемы либо сделал парафазные сигналы на входах 9 и 4 U1, например на 2-х элементах «исключающее ИЛИ» (их можно использовать как управляемые инверторы, один включить инвертором, второй — повторителем, входной сигнал — общий) вместо одного U1D. Так как задержки распространения сигналов через элементы на одном кристалле практически одинаковые, то «иголка» на выходе схемы должна будет исчезнуть… По-моему так 🙂

Ошибка, естественно не в медленной логике, а в моих руках использование логики разных скоростей — это «костыль», позволяющий не переделывать плату после того, как я лажанул.

НУ тогда понятно… 🙂 У нас в таких ситуациях обычно делали на разведенных платах небольшой кусочек макетной платы, куда можно было добавить пару корпусов для исправления найденных проблем. Монтаж там ведется на проводках, которые затем можно приклеить к плате лаком. Не могу припомнить ни одного случая, чтобы это не пригодились при настройке… 🙂 Конечно, после отладки опытных образцов платы переделывались, для серии они уже были без этих макетных участков, но зато и опытный образец работал как надо.

Для исключения таких казусов и придумали ПЛИСы. В новых разработках можно заложить вместо этого что-то типа EPM7032 и там уже смело экспериментировать.

Изначально, я это делал на xc9536. Но есть пару сообщений о том, что рядом с сильными магнитными полями содержимое flash-памяти может слететь. Не знаю, на сколько это правда, но так как схема простая, просто сделал ее на чистой логике.

Ну, если это некий шим-драйвер то зачем изобретать велосипед? Их же есть на любой вкус и цвет, от простых со внешними ключами, до полностью интегрированных, включая катушку на кристалле.

Веловипед, потому, что не нашел такого, как мне нужно. Собственно, вот он во всей красе:

https://bsvi.me/utc-datasheet/